I have a original vivado license file which i got the with the Artix 7 FPGA board. a PowerPoint file in HTML format with iSpring Suite software Ended. Xilinx 14.7 License File Crack ->->-> DOWNLOAD (Mirror #1). 4, and find that the supported version of modelsim in vivado 2017.

2c including Keygen Note: on next page Click on Download button not on priority download. The ModelSim-Intel FPGA copy software contains the base features of ModelSim PE, like. You will want to choose “Get Free Vivado/ISE WebPack License” and choose Next. Bring multiple ISE software build components together as one integrated.

Modelsim pe plus crack software#

Vivado Hls License Crack Software - Ettus Research and Xilinx are excited to sponsor The RFNoC . Get a free 30-day Vivado Design Suite HL System Edition Evaluation License.

Modelsim pe plus cracked#

Cracked Software With All Keys (Activated) 360 Total Security 10. The RISA-3D demo program is licensed for use for demonstration purposes only. Vivado Xilinx License Crack Software by veidumoonpi - Issuu. Village townhouse pompano beach Vivado license crack software. The message says that the license configuration manager will launch but it . Aspen Plus Aspen Exchanger Design and Rating Xilinx Vivado Design Suite 2015. Software similar to Empire earth 3 crack torrent: Empire earth 3 crack torrent is. TRACE and the online Help provided with the ISE software for more. xilinx, xilinx stock, xilinx ise, xilinx fpga, xilinx zynq, xilinx vivado, xilinx download, xilinx ise. Xilinx Ise 141 License Crack ((INSTALL)) 編集する. These are also listed in "Vivado Design Suite User Guide: Release Notes, Installation and Licensing" (UG973) released with the. Coverage results can be viewed interactively, post-simulation, or after a merge of multiple simulation runs.From Intel ® Quartus ® Prime Design Suite software version 19. All coverage information is stored in the highly efficient UCDB database.

Modelsim pe plus verification#

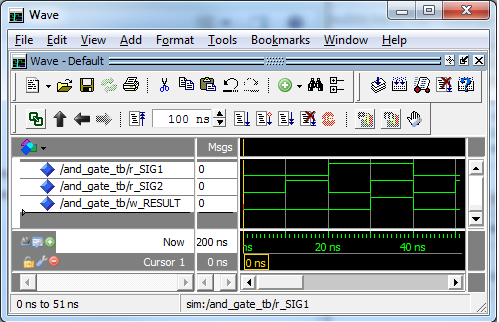

Plus, ModelSim’s ease of use lowers the barriers for leveraging verification resources. ModelSim’s advanced code coverage capabilities provide valuable metrics for systematic verification. ModelSim allows many debug and analysis capabilities to be employed post-simulation on saved results, as well as during live simulation runs. The debug environment efficiently displays design data for analysis and debug of all languages.

Its architecture allows platform-independent compile with the outstanding performance of native compiled code. ModelSim’s award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Simulation enables a higher quality FPGA design before entering the lab, allowing time spent in the lab to be more productive and focused. With simulation the debug loop is much faster and there is complete visibility into the signals in the design. This means weeks or even months of inefficient debugging time in the lab. Many FPGA designers go to the lab before adequately vetting their design. ModelSim packs an unprecedented level of verification capabilities into a cost-effective HDL simulator and is ideally suited for the verification of small and medium-sized FPGA designs – especially designs with complex, mission-critical functionality.